![]() ## 硬件纹理压缩:一个新时代

硬件图像格式的创新历来缓慢,受到广泛硬件支持需求阻碍。然而,新的实时和硬件压缩技术正在改变这一局面。实时压缩允许更快地引入格式,因为它绕过了对现有内容的依赖。

目前,三种主要的硬件压缩格式正在出现:苹果的无损压缩(A15/M2芯片)、ARM的AFRC(Mali-G715/G615)和ImgTec的PVRIC4(Pixel 10)。苹果的格式易于实现,提供1:2压缩,质量良好,可与现有编解码器相媲美。ARM的AFRC以其灵活的压缩比和卓越的质量脱颖而出,甚至超过了实时ASTC编码。ImgTec的PVRIC4目前默认使用1:2压缩,测试表明质量较低。

性能测试表明,硬件压缩可以饱和内存带宽,通常与软件解决方案(如Spark)的速度相匹配或超过,尤其是在带宽受限的设备上。虽然AFRC目前在质量和性能方面领先,但硬件压缩仍然仅限于较新的设备。

最终,硬件压缩提供了一种引人注目的替代方案,但跨厂商的一致质量仍然是一个挑战,这使得像Spark这样的解决方案对于可预测的结果和潜在的未来WebGPU集成具有价值。

## 硬件纹理压缩:一个新时代

硬件图像格式的创新历来缓慢,受到广泛硬件支持需求阻碍。然而,新的实时和硬件压缩技术正在改变这一局面。实时压缩允许更快地引入格式,因为它绕过了对现有内容的依赖。

目前,三种主要的硬件压缩格式正在出现:苹果的无损压缩(A15/M2芯片)、ARM的AFRC(Mali-G715/G615)和ImgTec的PVRIC4(Pixel 10)。苹果的格式易于实现,提供1:2压缩,质量良好,可与现有编解码器相媲美。ARM的AFRC以其灵活的压缩比和卓越的质量脱颖而出,甚至超过了实时ASTC编码。ImgTec的PVRIC4目前默认使用1:2压缩,测试表明质量较低。

性能测试表明,硬件压缩可以饱和内存带宽,通常与软件解决方案(如Spark)的速度相匹配或超过,尤其是在带宽受限的设备上。虽然AFRC目前在质量和性能方面领先,但硬件压缩仍然仅限于较新的设备。

最终,硬件压缩提供了一种引人注目的替代方案,但跨厂商的一致质量仍然是一个挑战,这使得像Spark这样的解决方案对于可预测的结果和潜在的未来WebGPU集成具有价值。

每日HackerNews RSS

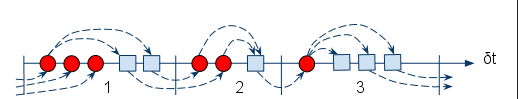

## VHDL 与 Verilog:确定性的关键

本文重点介绍了 VHDL 和 Verilog 之间的一个关键区别:**确定性**。VHDL 通过其“delta 循环”算法实现可预测的结果。该系统将信号更新和过程评估分为不同的阶段。信号更新首先发生,触发过程,然后过程更新信号——但这些更新被安排在*未来*的 delta 循环中。这确保了过程始终看到信号值的稳定快照,无论每个阶段内的执行顺序如何,从而保证了确定性的结果。

Verilog 缺乏这种分离。信号更新和过程评估可以交错进行,这意味着过程可能会根据执行顺序观察到不同的值,从而导致非确定性行为。虽然 Verilog 的非阻塞赋值*延迟*更新,但它们并未强制执行 VHDL 的分阶段方法。

作者认为 VHDL 的 delta 循环是其最强大的特性,以最小的开销提供内置的确定性。虽然 Verilog 可以通过使用非阻塞赋值在特定的同步设计中实现确定性,但这并非普遍保证。VHDL 依赖于信号进行过程间通信,而信号本质上利用了 delta 循环,这有助于其一致的行为,与 Verilog 依赖 `reg` 类型以及阻塞赋值与非阻塞赋值的复杂性形成了鲜明对比。

## VHDL 与 Verilog:确定性的关键

本文重点介绍了 VHDL 和 Verilog 之间的一个关键区别:**确定性**。VHDL 通过其“delta 循环”算法实现可预测的结果。该系统将信号更新和过程评估分为不同的阶段。信号更新首先发生,触发过程,然后过程更新信号——但这些更新被安排在*未来*的 delta 循环中。这确保了过程始终看到信号值的稳定快照,无论每个阶段内的执行顺序如何,从而保证了确定性的结果。

Verilog 缺乏这种分离。信号更新和过程评估可以交错进行,这意味着过程可能会根据执行顺序观察到不同的值,从而导致非确定性行为。虽然 Verilog 的非阻塞赋值*延迟*更新,但它们并未强制执行 VHDL 的分阶段方法。

作者认为 VHDL 的 delta 循环是其最强大的特性,以最小的开销提供内置的确定性。虽然 Verilog 可以通过使用非阻塞赋值在特定的同步设计中实现确定性,但这并非普遍保证。VHDL 依赖于信号进行过程间通信,而信号本质上利用了 delta 循环,这有助于其一致的行为,与 Verilog 依赖 `reg` 类型以及阻塞赋值与非阻塞赋值的复杂性形成了鲜明对比。

## Windows 98SE/ME 高清音频驱动 – 概要 该项目旨在为 Windows 98SE 和 ME 系统带来高清 (HD) 音频支持,特别是针对 Intel 915 及更新芯片组,*没有* AC97 音频的系统。 目前这是一个处于 Alpha 阶段的驱动程序,可在虚拟机 (VMware, VirtualBox) 以及部分 Intel/VIA 芯片组系统(使用瑞昱编解码器)上运行。 **重要限制:** 它仅*官方*支持 98SE/ME,Windows 98 第一版已知存在问题。 Windows 2000/XP 具有原生支持,不需要此驱动程序。 预计可能存在不稳定情况 – 音频失真、冻结或静音是常见问题。 **对于关键应用,强烈建议使用 USB 音频扩展坞。** 该驱动程序仅支持播放(不支持录音),限制为 22-48kHz 16 位音频,并且具有明显的延迟 (~40ms)。 它依赖于 BIOS 设置,并且缺乏对错误配置的覆盖。 开发正在进行中,重点是提高硬件兼容性(目前 Nvidia/AMD 和某些编解码器支持较差)。 调试信息和构建说明可在项目的 Github 页面上找到。

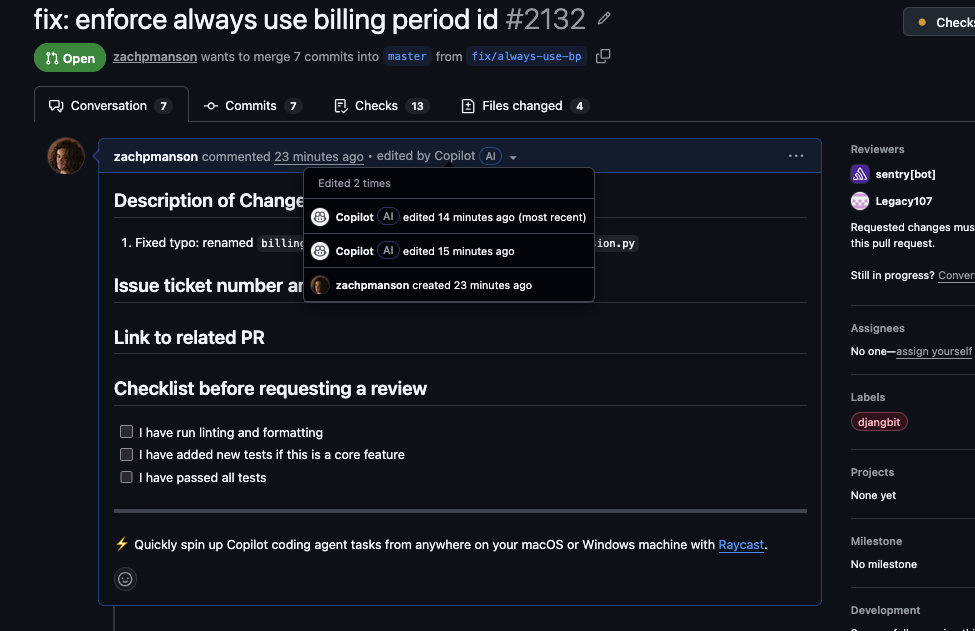

一位团队成员调用Copilot为我的PR中的一个错别字进行修正,结果Copilot编辑了我的PR描述,添加了关于它自己和Raycast的广告。这太可怕了。我知道这种事情迟早会发生,但我没想到会这么快。平台衰败的方式是这样的:首先,它们对用户很好;然后,它们为了商业客户的利益而滥用用户;最后,它们为了自己攫取所有价值而滥用这些商业客户。然后,它们就衰败了。科里·道克托罗

一位团队成员调用Copilot为我的PR中的一个错别字进行修正,结果Copilot编辑了我的PR描述,添加了关于它自己和Raycast的广告。这太可怕了。我知道这种事情迟早会发生,但我没想到会这么快。平台衰败的方式是这样的:首先,它们对用户很好;然后,它们为了商业客户的利益而滥用用户;最后,它们为了自己攫取所有价值而滥用这些商业客户。然后,它们就衰败了。科里·道克托罗

关于 新闻 版权 联系我们 创作者 广告 开发者 条款 隐私政策和安全 YouTube 工作原理 测试新功能 © 2026 Google LLC

这个项目探讨了一个基本问题:剥离文化假设后,时钟*到底*是什么?答案出乎意料地在于几何学。时钟需要一个可重复的过程、一个计数规则、与时间标度的校准,以及一个可读的映射——从物理学精确的持续时间到民用时间对社会需求的层次。大多数时钟混淆了这些层次。 目标是从第一性原理重新发明时钟,优先考虑清晰度和通用性。解决方案采用基于多边形的编码,其中每个数字(0-9)由一个具有相应顶点数量的多边形表示。该系统与方向无关,在镜子或零重力环境下也能同样良好地工作。 六个同心圆显示小时、分钟和秒,并经过精心设计,以防止视觉重叠。一个24小时的弧线提供了一天的时间比例视图,类似于日晷,无需读取数字即可提供即时背景。严格的测试证实了在一天中的所有86,400秒内准确计时。该设计名为“Gonon”(源自希腊语中的“角度”,指的是其几何基础),旨在以符合人类感知的方式呈现时间——比例用于感知,精确用于安排——提供了一种全新的“时间观”。

请启用 JavaScript 并禁用任何广告拦截器。

## 量子控制平面:开发者平台概要

量子控制平面 (QCP) 是一个开源开发者平台,旨在简化量子计算工作流程,类似于 MLflow 或 Airflow。它提供了一个 SDK、CLI 和 REST API,用于提交 QASM 电路、编排实验、基准测试提供商以及可视化结果。

QCP 结构分为三个层面:**控制平面**(管理实验、工作流和成本)、**执行平面**(通过工作节点、提供商和模拟器运行作业)以及用于监控和分析的 **仪表盘**。

主要功能包括提供商抽象、电路优化以及基于 PostgreSQL、Redis 和 Prometheus & Grafana 等可观察性工具构建的强大基础设施。快速入门指南方便使用 Docker 或轻量级本地开发环境进行快速设置。

该平台支持通过提供商插件扩展功能,并包含演示纠缠(贝尔态和 GHZ 态)和格罗弗搜索算法的示例实验。代码检查、类型检查和测试等开发工具通过 `make` 命令集成。

![]() ## macOS M4/M5 4K 显示器 HiDPI 回归

近期,搭载 M4 和 M5 Apple Silicon 芯片的 macOS 版本出现了一个限制,导致 4K 外接显示器无法实现完全分辨率的 HiDPI(高点密度)缩放。虽然硬件支持 – M5 Max 可以原生处理 8K – 但 3840x2160 显示器的可用最高 HiDPI 模式现在是 3360x1890,迫使用户在清晰的文本和减少的屏幕空间之间做出选择,或者使用完整的 4K 分辨率但文本模糊。

这不是硬件问题;M2/M3 和 M4/M5 机器报告的显示能力相同。问题在于 GPU 驱动程序 (AppleDisplayCrossbar),它现在将 HiDPI 后备存储限制在原生分辨率的约 1.75 倍,而不是实现真正的 4K HiDPI 所需的 2.0 倍。大量的故障排除,包括 EDID 补丁和 IOKit 注册表覆盖,已经证实该限制是由该驱动程序的显示模式生成策略强制执行的。

该驱动程序似乎正在实施保守的帧缓冲区分配策略,为潜在的附加显示器保留资源。修复需要 Apple 根据*实际*连接的显示器智能管理帧缓冲区分配,或者提供用户覆盖选项。鼓励用户向 Apple 提交反馈,并参考 BetterDisplay 讨论 #4215。

## macOS M4/M5 4K 显示器 HiDPI 回归

近期,搭载 M4 和 M5 Apple Silicon 芯片的 macOS 版本出现了一个限制,导致 4K 外接显示器无法实现完全分辨率的 HiDPI(高点密度)缩放。虽然硬件支持 – M5 Max 可以原生处理 8K – 但 3840x2160 显示器的可用最高 HiDPI 模式现在是 3360x1890,迫使用户在清晰的文本和减少的屏幕空间之间做出选择,或者使用完整的 4K 分辨率但文本模糊。

这不是硬件问题;M2/M3 和 M4/M5 机器报告的显示能力相同。问题在于 GPU 驱动程序 (AppleDisplayCrossbar),它现在将 HiDPI 后备存储限制在原生分辨率的约 1.75 倍,而不是实现真正的 4K HiDPI 所需的 2.0 倍。大量的故障排除,包括 EDID 补丁和 IOKit 注册表覆盖,已经证实该限制是由该驱动程序的显示模式生成策略强制执行的。

该驱动程序似乎正在实施保守的帧缓冲区分配策略,为潜在的附加显示器保留资源。修复需要 Apple 根据*实际*连接的显示器智能管理帧缓冲区分配,或者提供用户覆盖选项。鼓励用户向 Apple 提交反馈,并参考 BetterDisplay 讨论 #4215。

## 开源操作系统与年龄验证:摘要 包括巴西和加利福尼亚州在内的多个地区正在制定法律,要求操作系统实施年龄验证。本页面跟踪开源操作系统(Linux、*BSD 等)对这些不断变化的法规的响应。 目前,**没有开源操作系统完全符合**巴西或加利福尼亚州的年龄验证法律。 该列表对操作系统响应进行分类:一些开发者**不实施**验证,并可能限制在受影响地区的访问。另一些开发者**计划实施**它,但功能仍在开发中。 科罗拉多州、伊利诺伊州、纽约州和密歇根州等州的拟议立法可能会进一步扩大这些要求。本文档作为开源社区应对这些新的法律挑战的持续更新。